- SYSTEMVERILOG TESTBENCH FOR PARALLEL TO SERIAL CONVERTER HOW TO

- SYSTEMVERILOG TESTBENCH FOR PARALLEL TO SERIAL CONVERTER FULL

- SYSTEMVERILOG TESTBENCH FOR PARALLEL TO SERIAL CONVERTER SERIES

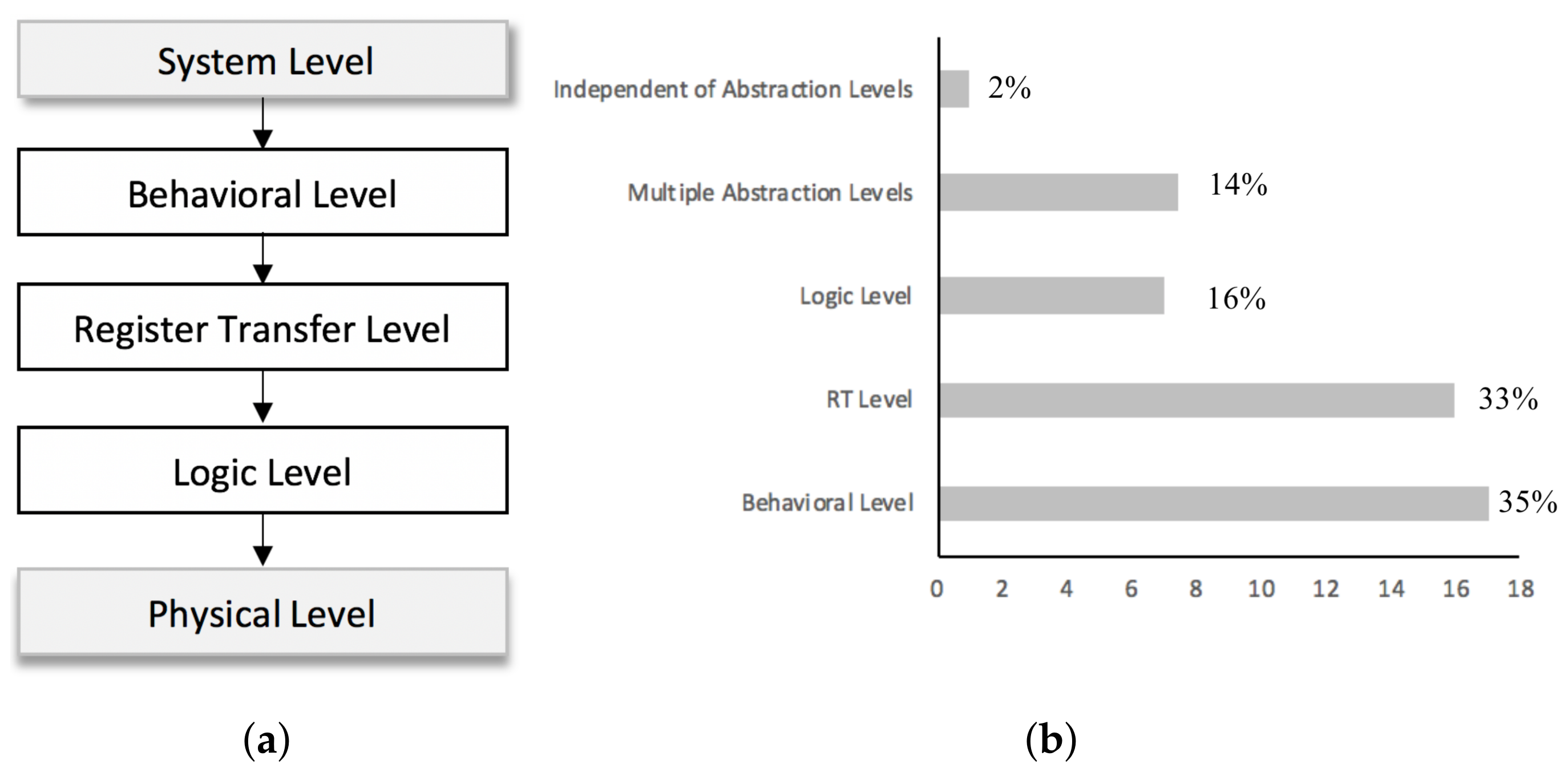

Behavioral simulation has little concept of how a design may actually be implemented in hardware and no concept of routing delays netlist simulation knows how the design is implemented, but is likewise ignorant of routing delays.

A wonderful thing, yes? Unfortunately, not only would you have to significantly modify this testbench each time the input was changed, but time does not always hold a fixed meaning in the context of simulation. This type of testbench could then “automatically” detect errors. You could even write a testbench that painstakingly describes each output waveform and tests specific values of the waves at strategic points in time. You could dump thousands of lines of text to disk, thus requiring someone to examine each and every message – likewise tedious and error-prone. The question becomes, after the simulation has run, how do you verify that it was successful – that the generated output matches the predicted output as driven by the stimulus? Certainly you could pore over many dozens to hundreds (or thousands) of waveforms, but this is extraordinarily tedious and time-consuming, not to mention error-prone. There are certainly many ways to create a stimulus set and drive it into the simulation – direct input from the simulation console, input from a text or binary file, scripted stimulus (.do or.

SYSTEMVERILOG TESTBENCH FOR PARALLEL TO SERIAL CONVERTER FULL

Given a known set of stimuli, a design should always produce a predictable collection of results – regardless of whether the simulation is behavioral, netlist or full timing (post place-and-route). Indeed, verifying a significant FPGA design can be more difficult and time-consuming than creating the synthesizable design.

While tolerable for a small design, this is a painful and ineffective means of verifying a larger, more sophisticated design. That would be 256 values for increment and another 256 for the decrement, along with the special cases of enable off and reset and how these control signals affect the count value. Now we can see the values of the outputs, but we also need to validate each and every single value. Zoomed-in waveform shows details, but no context. Zoomed-out waveform shows “big picture,” but lacksĭetails. How clearly do you see the results? Do you see the values ascending, then descending on the count_out_pins? What if we zoom in (blown-up circle)?įigure 2. Figure 2 shows a quick screen shot of the waveform view, both zoomed in and zoomed out.

SYSTEMVERILOG TESTBENCH FOR PARALLEL TO SERIAL CONVERTER SERIES

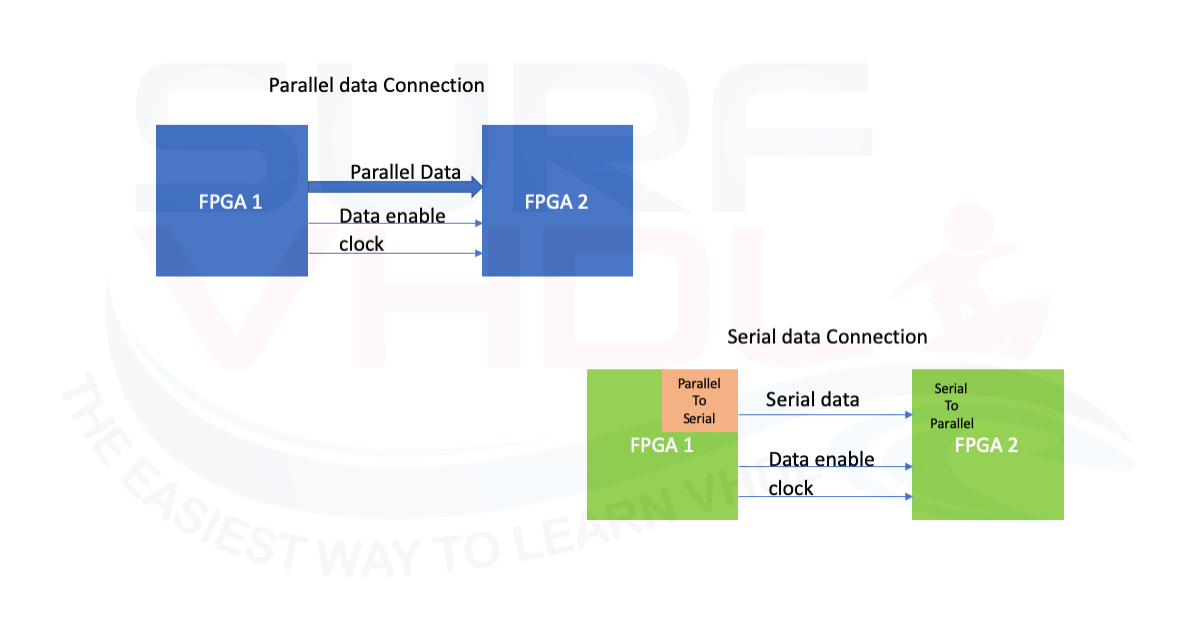

The various functions on the left side of the diagram provide stimulus for the UUT which, in turn, produces a series of waveforms displayed in the simulation environment.

SYSTEMVERILOG TESTBENCH FOR PARALLEL TO SERIAL CONVERTER HOW TO

Figure 1 shows how to connect the UUT (central gray box) to a testbench. The testbench provides clock, up/down, enable and reset control signals. Here’s quick example to illustrate how to implement a testbench using a simple 8-bit up/down with reset as the FPGA design (UUT). You can view both the stimulus and the reaction as waveforms in the simulation environment. These stimuli cause the UUT to react and interact with the virtual components. Simulation enables a unit under test (UUT) – typically, your synthesizable FPGA design – to connect to virtual (simulated) components such as memory, communication devices and/or CPUs, and be driven with a known set of stimuli. Editor’s Note: This article first appeared in the Winter 2012 edition of Xilinx's quarterly Xcell Journal magazine, and is reproduced here with their kind permission ( Click Here to see the magazine).Ī testbench, as it’s known in VHDL, or a test fixture in Verilog, is a construct that exists in a simulation environment such as ISim, ModelSim or NCsim.

0 kommentar(er)

0 kommentar(er)